Kernel examples • Percpu counters (vm statistics f.e, network statistics etc) Page allocator Slab allocators Various VFS components (buffer\_heads, counters) Irq tracking Rcu infrastructure Profiling, ftrace etc

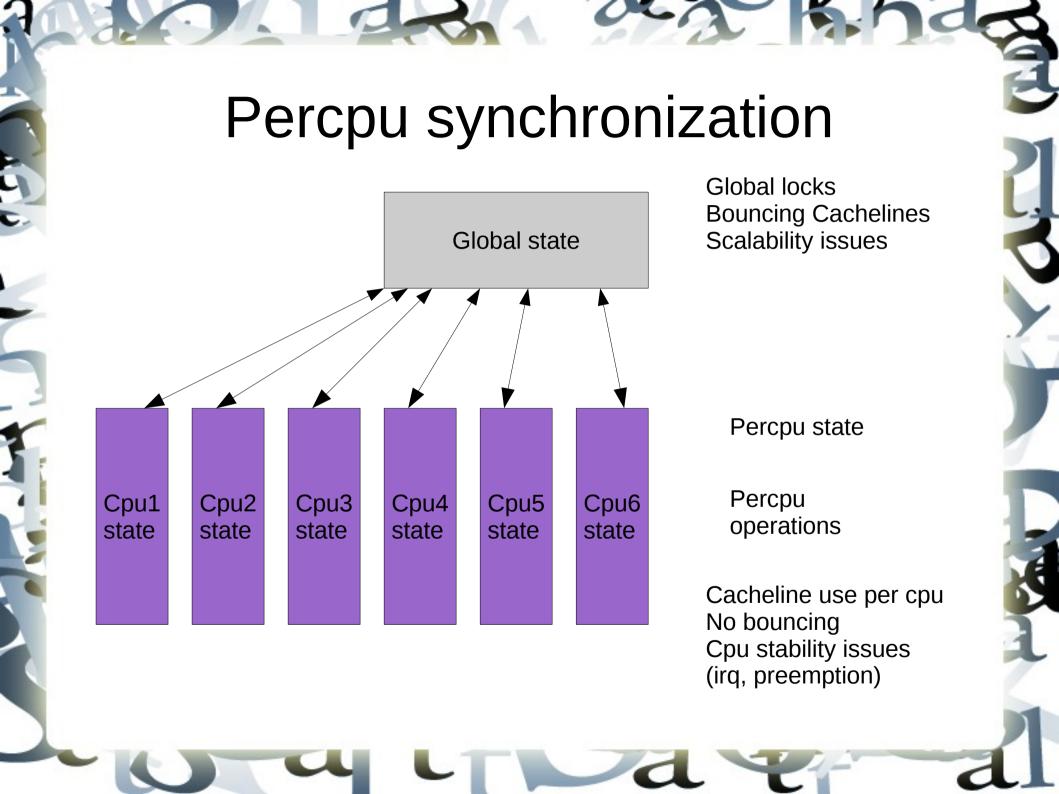

What are per cpu accesses Operations on data that is for use by a specific processor. OS keeps an instance of each variable for each processor. Per cpu accesses must relocate addresses to point to the right variable for this processor. Per cpu data is fast since cacheline bouncing does not occur. Per cpu variables can be effectively cached by the processor

Per cpu "atomicity" Concurrency issues exist but only on a single processor. In a preemptible environment the scheduler can give the processor to a different cpu (the currently executing code is interrupted) Interrupts can cause execution of different code. An "atomic" access is therefore an operation that is not subject to hardware interrupts. Ordering is not an issue since the view of a single cpu of the memory is guaranteed to be consistent. Percpu rmw instructions can avoid having to disable interrupts and/or preemption.

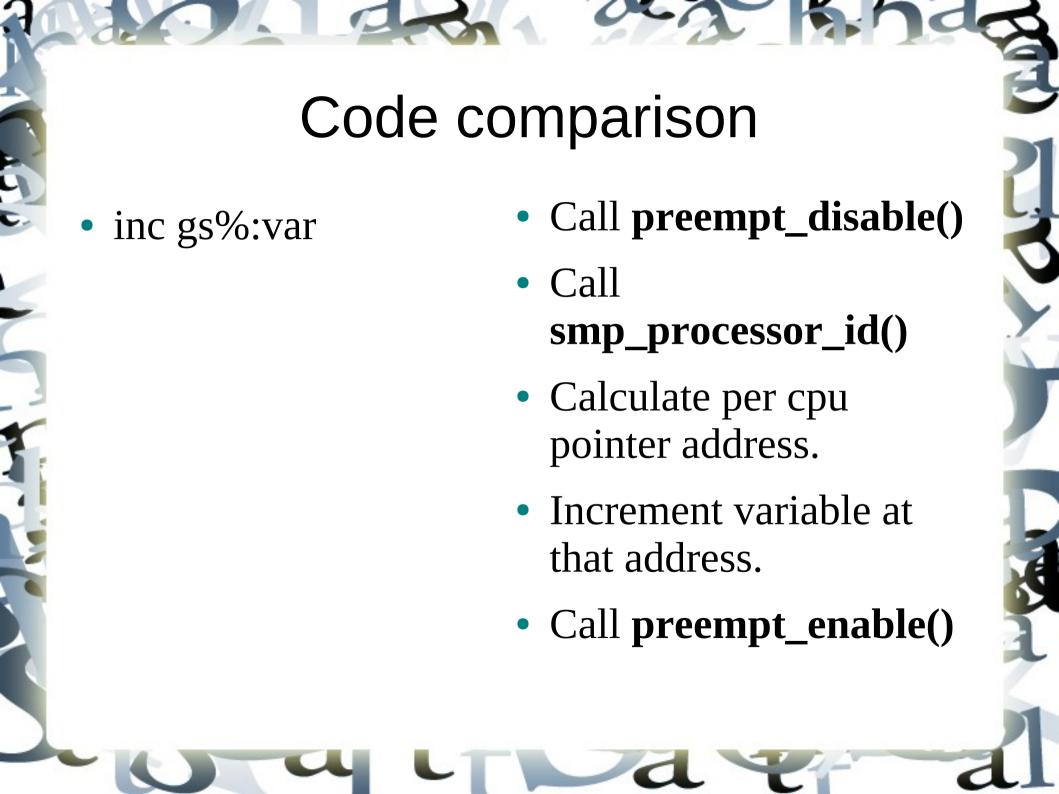

Example: this cpu\_inc(mycounter); → DECLARE\_PER\_CPU(mycounter, int) this\_cpu\_inc(mycounter) • There are NR CPUS instances of **mycounters**. • **this\_cpu\_inc** increments the one for the current processor. this\_cpu\_inc creates an instruction that guarantees the load and the store of the integer occur on the same processor. In many cases the processor has such instructions.

Open coded variant DECLARE\_PER\_CPU(int, mycounter); int cpu; preempt\_disable(); cpu = smp\_processor\_id(); per\_cpu(mycounter, cpu) += 1; preempt\_enable();

Simple per cpu operations this\_cpu operations work on variables not on pointers. this\_cpu\_load this\_cpu\_store this\_cpu\_inc this\_cpu\_add this\_cpu\_dec

Static per cpu declarations DECLARE\_PER\_CPU DEFINE PER CPU Address can be directly put into the inc instruction. No register use.

Dynamic per cpu allocations alloc\_percpu() Reserves memory in per cpu system areas. Returns a "percpu" pointer. Pointer cannot be directly dereferenced. It must first be relocated to a per cpu area using this\_cpu\_ptr() or per\_cpu\_ptr().

Incremented fields in dynamically allocated per cpu data • Fields can be directly specified. • Assume that p is a percpu pointer to struct structx with an int y in it. A percpu pointer can be obtained using either alloc\_percpu() Or & operator on a static per cpu variable Then the int y can be incremented using; - this\_cpu\_inc(structx->y)

Cmpxchg support Cmpxchg is useful to avoid disabling interrupts and preemption to update a value. Vm statistics use that

cmpxchg double support cmpxchg\_double can do atomic operations on a two wordsize variable Used by slub for pointer list management. One word contains the pointer Second word is a ticket number to be able to check if there was an operation in between. Must be emulated on ancient early AMD64 machines that did not have that instructions. Only effective on x86. Other arches have to fallback to a some code that simulates the action.

Slub fastpath use of cmpxchg double • Use of the ticket number to serialize pointer list operations. Avoids interupt disable and thereby cuts the cycle count in half. Barrier() instead of smp\_read/write\_barriers. Instruction placement matters. • The issue is that the processor may interrupt after each instruction.

Future endeavors Page allocator fastpath VFS? Restructuring of other subsystems to offload from global state to a local per cpu state Operate with per node state to avoid cross socket scalability issues (common 13 cache contention is less of a problem). "Segmentation" of the system to varying degrees in order to avoid locking overhead. Dedicated "servers" in kernel space to avoid cacheline pollution.